1. Kondisi[kembali]

Percobaan 4, Kondisi 2:

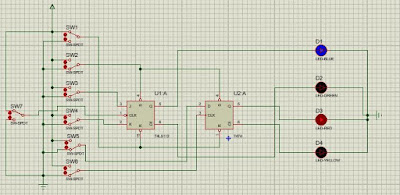

Buat rangkaian J-K flip flop dan D flip flop seperrti pada gambar pada percobaan dengan ketentuan input B0=1, B1=0, B2=don’t care, B3=don’t care, B4=don’t care, B5=don’t care, B6=don’t care.

2. Gambar Rangkaian[kembali]

3. Video Simulasi[kembali]

4. Prinsip Kerja[kembali]

Rangkaian dalam flip-flop dapat dilihat dari gambar dibawah ini beserta tabel kebenarannya

jadi pada saat kedua input bernilai 0 maka output yang dihasilkan tidak berubah. Pada input yang bernilai 0 pada J dan 1 pada K akan menghasilkan output Q=0 dan Q'=1. Sedangkan ketika input J bernilai 1 dan K bernilai 0 menghasilkan Output Q=1 dan Q'=0. Ketika nilai kedua input bernilai 1 maka output yang dihasilkan yaitu Toogle. Toogle berarti output yang dihasilkan akan berkebalikan dari posisi sebelumnya .

Flip-flop D merupakan modifikasi dari flip-flop JK. Untuk bentuk rangkaian dari flip-flop D dapat dilihat pada gambar di bawah ini.

Untuk tabel kebenaran dari flip-flop D dapat dilihat pada tabel kebenaran di bawah ini.

Pada Flip-flop D hanya ditemukan 2 kondisi yang sama dengan kondisi flip flop JK bernilai input berbeda. Hal itu karena Input dari flip flop D di paralelkan terhadap input J dan Inverter terhadap K. Hal tersebut sama artinya dengan Flip Flop JK yang hanya memiliki kondisi pada J dan K yang berlawanan nilai.

5. Link Download[kembali]

Rangkaian [di sini]

Video [di sini]

HTML [di sini]

Tidak ada komentar:

Posting Komentar